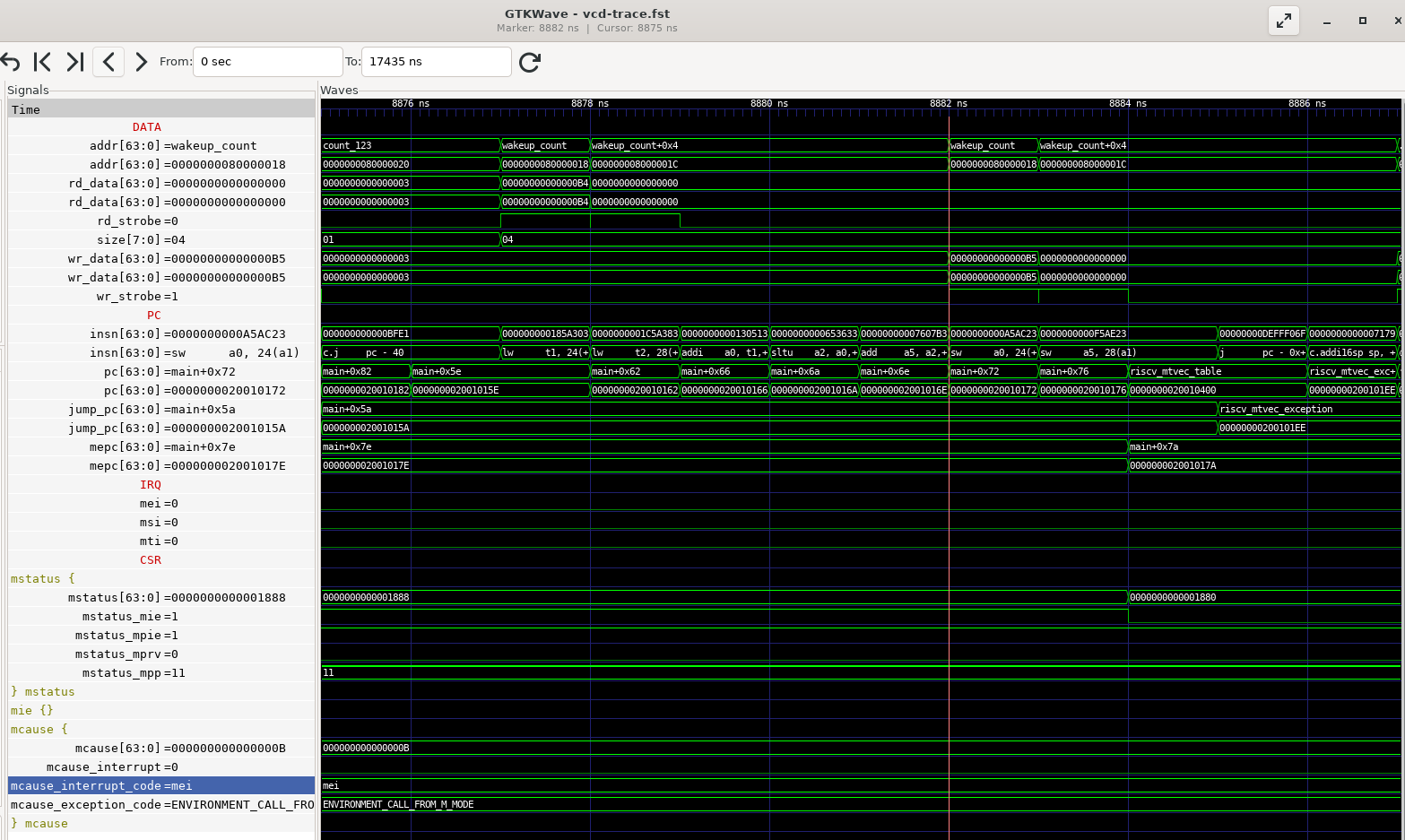

GTKWave Filters for Debugging VCD Traces of RISC-V Software

April 21, 2024 (toolchain,vcd,simulation,debugging,tracing,baremetal,C,gtkwave)

GTKWave can be used for firmware debugging. This is obviously useful for co-simulation, but is also useful for debugging timing and integration problems.

In a previous post I showed how to create a vcd trace of a firmware run via a fork of the RISC-V ISA simulator.

In this post using https://github.com/five-embeddev/riscv-gtkwave I add:

- Instruction Decoding according to the Spike disassembler.

- Bus Address decoding according to an elf file.

- CSR register decoding.

There are a few methods to decode via GTKWave. The decoders in https://github.com/five-embeddev/riscv-gtkwave are using 3 methods:

- Generated Translate filter file.

- Translate Filter process.

- Signal Grouping and Vector Expansion and Combination

Rust CSR Access Macros

December 28, 2022 (toolchain,baremetal,rust)

Added CSR access macros for RISC-V to the https://github.com/five-embeddev/riscv-csr-access respository.

- riscv-csr-access:rs/riscv_csr_macros/src/riscv_csr_macros.rs : Access macros

- riscv-csr-access:templates/riscv_csr_macros.rs: Generator Template

There is a standard crate for RISC-V https://docs.rs/riscv/0.1.4/riscv/index.html . that has a more canonical implementation for accessing CSRS. The purpose of this code is a to have a template generated implementation that closely matches the C header used for other examples riscv-csr-access:include/riscv-csr.h.

Rust CSR Access Macros

December 27, 2022 (toolchain,baremetal,rust)

Added CSR access macros for RISC-V to the https://github.com/five-embeddev/riscv-csr-access respository.

- riscv-csr-access:rs/riscv_csr_macros/src/riscv_csr_macros.rs : Access macros

- riscv-csr-access:templates/riscv_csr_macros.rs: Generator Template

There is a standard crate for RISC-V https://docs.rs/riscv/0.1.4/riscv/index.html . that has a more canonical implementation for accessing CSRS. The purpose of this code is a to have a template generated implementation that closely matches the C header used for other examples riscv-csr-access:include/riscv-csr.h.

Testing Startup Constructors

November 19, 2022 (toolchain,baremetal,C,C++)

There were a few bugs in the code examples that have been fixed.

The loop in startup.c function _startup() that calling each entry

from __init_array_start to __init_array_end was incorrect in

Startup Code in C and Startup Code in

C++. It has been fixed and tested.

To test it the main.c routine was updated to demonstrate the operation of the

contructors called in _startup() before main() is called.

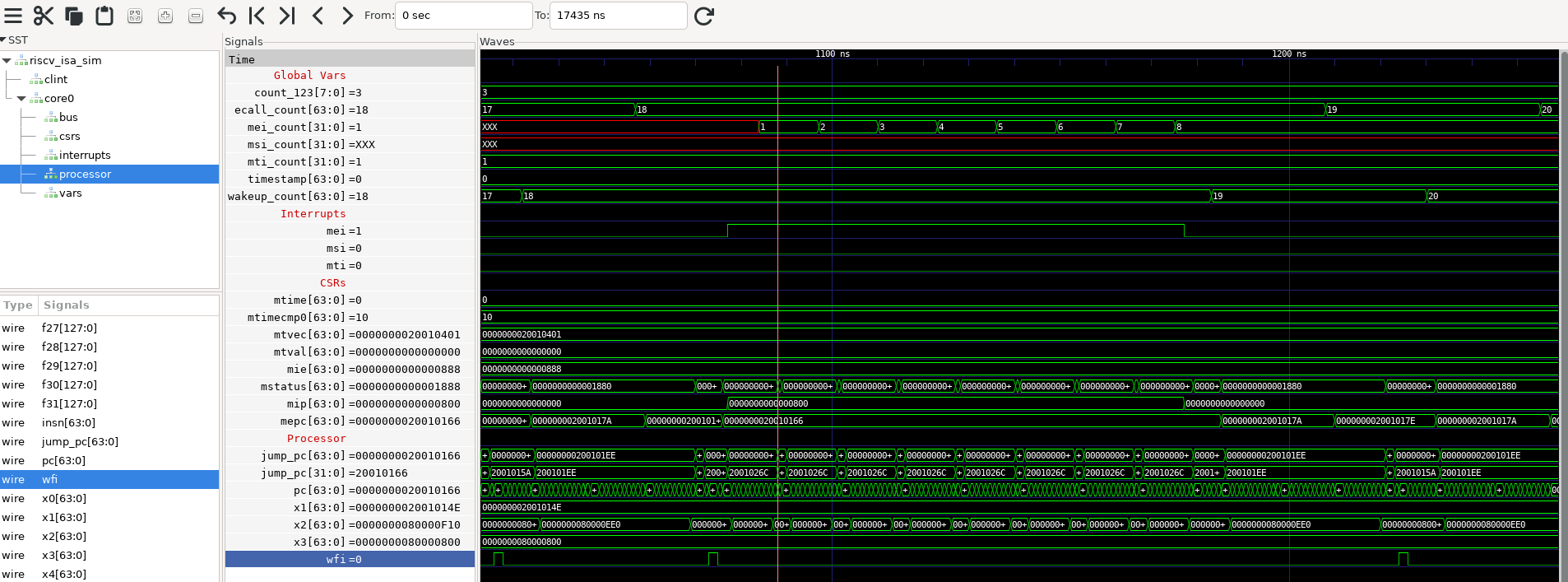

Example for VCD Tracing of RISC-V Software

September 04, 2022 (toolchain,vcd,simulation,debugging,tracing,baremetal,C)

In the previous post I added a fork of the RISC-V ISA simulator. In this post you can see how it can be used.

The source code for this example is on github, here: https://github.com/five-embeddev/riscv-scratchpad/tree/master/baremetal-vcd-trace.

This small program handles the mie, msi, mti and trap interrupts and updates some global variables when interrupts occur.

Baremetal Example Updates

September 01, 2022 (toolchain,baremetal,C,csr,registers,cmake)

Updates have been made to the baremetal examples.

CMake Updates

- The CMake file can now find

riscv-none-elf-gccas the xpack GCC executable has been renamed toriscv-none-elf-*. - Recent GCCs/binutils require the

zicsrextension to be specified in-marchto use CSR instructions.

Code Updates

- Updated CSR access templates to test for

zicsrextension. - Updated the CSR access header for the Baremetal C examples.

- Fixed the

CMakeLists.txtfiles to include-march=rv32imac_zicsr. - Updated the

timer.hto allow USEC/MSEC intervals and different timer frequencies. - Added the

baremetal-vcd-traceexample.

Example Bugs!

March 06, 2022 (toolchain,baremetal,C)

There were a few bugs in the code examples that have been fixed.

- Global pointer needs to be written with

norelaxoption set. (See quickref: Global Pointer) - For C++ the argument order to

std::copy()was incorrect. (it matchedmemcpy()… target, source)

Baremetal Vectored Interrupts in C for RISC-V

September 25, 2021 (articles,baremetal,C)

An example of using vectored interrupts in C.

Baremetal Timer Driver in C for RISC-V

September 24, 2021 (articles,baremetal,C)

An example of a timer driver in C has been added.

Baremetal Startup in C for RISC-V

September 24, 2021 (articles,baremetal,C)

An example of a startup code in C.

Baremetal Timer Driver in C++ for RISC-V

August 13, 2021 (articles,baremetal,C++)

An example of a timer driver.

Baremetal Interrupt in C++ for RISC-V

August 13, 2021 (articles,baremetal,C++)

An example of using interrupts.

Baremetal Programming in C++ for RISC-V

July 18, 2021 (toolchain,medium,baremetal,C++)

I’ve put together a series of posts on Medium covering bare-metal RISC-V development and C++.

- An overview of a simple bare-metal blinky application for the SiFive HiFive Rev-B

- Intro to PlatformIO for RISC-V

- Zero to

main()for RISC-V, in (almost) pure C++. - The CSR system registers of RISC-V and zero cost C++ abstractions.

- The RISC-V machine mode timer and timing keeping using the C++ std::chrono library.

- The basics of RISC-V interrupt handling, and C++ lambda functions.

(These are also included in this blog.)

Baremetal Startup Code in C++ for RISC-V

April 13, 2021 (toolchain,baremetal,C++)

An example of baremetal bootstrap code for RISC-V in C++.

RISC-V CSR Access

November 18, 2020 (registers,code,baremetal,quickref)

For baremetal programming I’ll often need to access CSRs, e.g. mstatus.mie for critical sections, mcause in interrupts handlers, etc. Defining function wrappers for accessing these registers creates easier to understand code, however writing these wrappers is pretty tedious.

The quick reference on this blog is generated from a YAML description (csr.yaml). Using that with a web template engine script (generators/yaml_jinja.py) and a template (templates/riscv-csr.h) code can be easily generated.

Five EmbedDev

Five EmbedDev